# Proteus Series Arbitrary Waveform Generator/ Transceiver Module User Manual

**Rev. 1.3**

#### Warranty Statement

Products sold by Tabor Electronics Ltd. are warranted to be free from defects in workmanship or materials. Tabor Electronics Ltd. will, at its option, either repair or replace any hardware products which prove to be defective during the warranty period. You are a valued customer. Our mission is to make any necessary repairs in a reliable and timely manner.

#### **Duration of Warranty**

The warranty period for this Tabor Electronics Ltd. hardware is one year, except software and firmware products designed for use with Tabor Electronics Ltd. Hardware is warranted not to fail to execute its programming instructions due to defect in materials or workmanship for a period of ninety (90) days from the date of delivery to the initial end user.

#### **Return of Product**

Authorization is required from Tabor Electronics before you send us your product for service or calibration. Call your nearest Tabor Electronics support facility. A list is located on the last page of this manual. If you are unsure where to call, contact Tabor Electronics Ltd. Tel Hanan, Israel at 972-4-821-3393 or via fax at 972-4-821-3388. We can be reached at: support@tabor.co.il

#### Limitation of Warranty

Tabor Electronics Ltd. shall be released from all obligations under this warranty in the event repairs or modifications are made by persons other than authorized Tabor Electronics service personnel or without the written consent of Tabor Electronics.

Tabor Electronics Ltd. expressly disclaims any liability to its customers, dealers and representatives and to users of its product, and to any other person or persons, for special or consequential damages of any kind and from any cause whatsoever arising out of or in any way connected with the manufacture, sale, handling, repair, maintenance, replacement or use of said products.

Representations and warranties made by any person including dealers and representatives of Tabor Electronics Ltd., which are inconsistent or in conflict with the terms of this warranty (including but not limited to the limitations of the liability of Tabor Electronics Ltd. as set forth above), shall not be binding upon Tabor Electronics Ltd. unless reduced to writing and approved by an officer of Tabor Electronics Ltd.

This document may contain flaws, omissions or typesetting errors. No warranty is granted nor liability assumed in relation thereto. The information contained herein is periodically updated and changes will be incorporated into subsequent editions. If you have encountered an error, please notify us at support@taborelec.com. All specifications are subject to change without prior notice.

Except as stated above, Tabor Electronics Ltd. makes no warranty, express or implied (either in fact or by operation of law), statutory or otherwise; and except to the extent stated above, Tabor Electronics Ltd. shall have no liability under any warranty, express or implied (either in fact or by operation of law), statutory or otherwise.

#### **Proprietary Notice**

This document and the technical data herein disclosed, are proprietary to Tabor Electronics, and shall not, without express written permission of Tabor Electronics, be used, in whole or in part to solicit quotations from a competitive source or used for manufacture by anyone other than Tabor Electronics. The information herein has been developed at private expense, and may only be used for operation and maintenance reference purposes or for purposes of engineering evaluation and incorporation into technical specifications and other documents, which specify procurement of products from Tabor Electronics.

# **Document Revision History**

| Revision | Date        | Description                                                                                                                                                     | Author                         |

|----------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| 1.3      | 11-Mar-2024 | <ul> <li>Release supporting WDS 1.7.050 or higher, SCPI<br/>Rev. 1.136, FPGA version 237 or higher.</li> </ul>                                                  | Joan Mercado<br>Jakob Apelblat |

|          |             | <ul> <li><u>1.2 Related Documentation</u> – New.</li> </ul>                                                                                                     |                                |

|          |             | <ul> <li><u>Table 2.1 Ordering Information</u> – Added P9482M,<br/>and P9484M</li> </ul>                                                                        |                                |

|          |             | <ul> <li><u>Table 2.2 Available Options for Proteus Series</u></li> <li><u>Module Platform</u> – Added G1 and G2.</li> </ul>                                    |                                |

|          |             | <ul> <li><u>2.2 Features and Highlights</u> – Updated.</li> </ul>                                                                                               |                                |

|          |             | <ul> <li><u>2.3 System Requirements</u> – Updated.</li> </ul>                                                                                                   |                                |

|          |             | • <u>2.4 Options</u> – Updated.                                                                                                                                 |                                |

|          |             | • <u>2.5.1 Proteus AWT Front Panel</u> – New.                                                                                                                   |                                |

|          |             | <ul> <li><u>Table 4.1 Proteus Models vs. GS/s</u> – Updated.</li> </ul>                                                                                         |                                |

|          |             | <ul> <li><u>Table 4.2 Waveform Sampling Rate Range vs. DAC</u><br/><u>Sampling Rate as a Function of the Interpolation</u><br/><u>Factor</u> – New.</li> </ul>  |                                |

|          |             | <ul> <li><u>6.3 Task Table Parameters</u> – New parameter<br/>Trigger ADC.</li> </ul>                                                                           |                                |

|          |             | • <u>8 DUC Operation</u> – New.                                                                                                                                 |                                |

|          |             | • <u>10 Digitizer</u> – New.                                                                                                                                    |                                |

|          |             | <ul> <li><u>12 Proteus Module Specifications</u> – Updated.</li> </ul>                                                                                          |                                |

| 1.2      | 05-Apr-2021 | • <u>1.3 Software Support</u> – New.                                                                                                                            | Jakob Apelblat                 |

|          |             | <ul> <li>Removed section "Programming". Refer to<br/>Proteus Programming Manual.</li> </ul>                                                                     |                                |

|          |             | <ul> <li>Removed sections "Minimum System<br/>Requirements" and "Wave Design Installation".<br/>Refer to WDS User Manual.</li> </ul>                            |                                |

|          |             | <ul> <li><u>12.7 Direct Output</u> – Changed amplitude from<br/>"600 mVpp" to "1 mVpp to 550 mVpp".</li> </ul>                                                  |                                |

| 1.1      | 28-Oct-2020 | <ul> <li>Changed page size to letter.</li> </ul>                                                                                                                | Jakob Apelblat                 |

|          |             | <ul> <li><u>12.16 Digitizer Characteristics (AWT Option)</u> –<br/>Changed Acquisition Memory from "&lt;2<br/>GS/channel" to "Up to max memory size"</li> </ul> |                                |

|          |             | <ul> <li>Removed WDS description and replaced it with a reference to the WDS User Manual.</li> </ul>                                                            |                                |

|          |             | <ul> <li><u>9.6.2 Internal Trigger</u> – New note.</li> </ul>                                                                                                   |                                |

|          |             | <ul> <li><u>12 Proteus Module Specifications</u> – Minor formatting.</li> </ul>                                                                                 |                                |

|          |             | • <u>14 Appendix Log File</u> – New.                                                                                                                            |                                |

| Revision | Date        | Description                                                                                 | Author          |

|----------|-------------|---------------------------------------------------------------------------------------------|-----------------|

| 1.0      | 15-Jul-2020 | <ul> <li>Original release supporting WDS version 1.2.192,<br/>FPGA version 1.2.0</li> </ul> | Jonathan Netzer |

# **Acronyms & Abbreviations**

| Acronym          | Description                                                                        |

|------------------|------------------------------------------------------------------------------------|

| μs or us         | Microseconds                                                                       |

| ADC              | Analog to Digital Converter                                                        |

| AM               | Amplitude Modulation                                                               |

| ASIC             | Application-Specific Integrated Circuit                                            |

| ATE              | Automatic Test Equipment                                                           |

| AWG              | Arbitrary Waveform Generators                                                      |

| AWT              | Arbitrary Waveform Transceiver                                                     |

| BNC              | Bayonet Neill–Concelm (coax connector)                                             |

| BW               | Bandwidth                                                                          |

| CW               | Carrier Wave                                                                       |

| DAC              | Digital to Analog Converter                                                        |

| dBc              | dB/carrier. The power ratio of a signal to a carrier signal, expressed in decibels |

| dBm              | Decibel-Milliwatts. E.g., 0 dBm equals 1.0 mW.                                     |

| DDC              | Digital Down-Converter                                                             |

| DHCP             | Dynamic Host Configuration Protocol                                                |

| DSO              | Digital Storage Oscilloscope                                                       |

| DUC              | Digital Up-Converter                                                               |

| ENoB             | Effective Number of Bits                                                           |

| ESD              | Electrostatic Discharge                                                            |

| EVM              | Error Vector Magnitude                                                             |

| EW               | Electronic Warfare                                                                 |

| F <sub>NCO</sub> | Numerically Controlled Oscillator Frequency                                        |

| FPGA             | Field-Programmable Gate Arrays                                                     |

| GHz              | Gigahertz                                                                          |

| GPIB             | General Purpose Interface Bus                                                      |

| GS/s             | Giga Samples per Second                                                            |

| Acronym | Description                                                    |

|---------|----------------------------------------------------------------|

| GUI     | Graphical User Interface                                       |

| НР      | Horizontal Pitch (PXIe module horizontal width, 1 HP = 5.08mm) |

| Hz      | Hertz                                                          |

| IF      | Intermediate Frequency                                         |

| I/O     | Input / Output                                                 |

| IP      | Internet Protocol                                              |

| IQ      | In-phase Quadrature                                            |

| IVI     | Interchangeable Virtual Instrument                             |

| JSON    | JavaScript Object Notation                                     |

| kHz     | Kilohertz                                                      |

| LCD     | Liquid Crystal Display                                         |

| LO      | Local Oscillator                                               |

| MAC     | Media Access Control (address)                                 |

| MDR     | Mini D Ribbon (connector)                                      |

| MHz     | Megahertz                                                      |

| MIMO    | Multiple-Input Multiple-Output                                 |

| ms      | Milliseconds                                                   |

| NCO     | Numerically Controlled Oscillator                              |

| ns      | Nanoseconds                                                    |

| PC      | Personal Computer                                              |

| РСАР    | Projected Capacitive Touch Panel                               |

| РСВ     | Printed Circuit Board                                          |

| PCI     | Peripheral Component Interconnect                              |

| PRBS    | Pseudorandom Binary Sequence                                   |

| PRI     | Pulse Repetition Interval                                      |

| PXI     | PCI eXtension for Instrumentation                              |

| PXIe    | PCI Express eXtension for Instrumentation                      |

| QC      | Quantum Computing                                              |

| Qubits  | Quantum bits                                                   |

| RADAR   | Radio Detection And Ranging                                    |

| R&D     | Research & Development                                         |

| Acronym | Description                                    |

|---------|------------------------------------------------|

| RF      | Radio Frequency                                |

| RT-DSO  | Real-Time Digital Oscilloscope                 |

| S       | Seconds                                        |

| SA      | Spectrum Analyzer                              |

| SCPI    | Standard Commands for Programmable Instruments |

| SFDR    | Spurious Free Dynamic Range                    |

| SFP     | Software Front Panel                           |

| SMA     | Subminiature version A connector               |

| SMP     | Subminiature Push-on connector                 |

| SPI     | Serial Peripheral Interface                    |

| SRAM    | Static Random-Access Memory                    |

| TFT     | Thin Film Transistor                           |

| T&M     | Test and Measurement                           |

| TPS     | Test Program Sets                              |

| UART    | Universal Asynchronous Receiver-Transmitter    |

| USB     | Universal Serial Bus                           |

| VCP     | Virtual COM Port                               |

| Vdc     | Volts, Direct Current                          |

| V р-р   | Volts, Peak-to-Peak                            |

| VSA     | Vector Signal Analyzer                         |

| VSG     | Vector Signal Generator                        |

| WDS     | Wave Design Studio                             |

# Contents

| 1 | Gene  | ral15                                                                                      |

|---|-------|--------------------------------------------------------------------------------------------|

|   | 1.1   | Scope                                                                                      |

|   | 1.2   | Related Documentation15                                                                    |

|   | 1.3   | Software Support15                                                                         |

|   | 1.4   | Document Conventions15                                                                     |

|   | 1.5   | 1.4.1 General                                                                              |

|   | 1.6   | Maintenance16                                                                              |

| 2 | Intro | 1.6.1Preventive Maintenance161.6.2Long Term Storage or Repackaging For Shipment16duction18 |

|   | 2.1   | Overview                                                                                   |

|   | 2.2   | Features and Highlights 20                                                                 |

|   | 2.3   | System Requirements                                                                        |

|   | 2.4   | Options                                                                                    |

|   | 2.5   | Front Panel                                                                                |

| 3 | Insta | 2.5.1 Proteus AWT Front Panel                                                              |

|   | 3.1   | Installation Overview                                                                      |

|   | 3.2   | Unpacking and Initial Inspection                                                           |

|   | 3.3   | Safety Precautions                                                                         |

|   | 3.4   | Operating Environment                                                                      |

|   | 3.5   | Performance Checks                                                                         |

|   | 3.6   | Power Requirements                                                                         |

|   | 3.7   | Grounding Requirements 29                                                                  |

|   | 3.8   | Calibration                                                                                |

|   | 3.9   | Abnormal Conditions                                                                        |

|   | 3.10  | Long Term Storage or Repackaging for Shipment                                              |

|   | 3.11  | Preparation for Use                                                                        |

|   |       | 3.11.1Removing the Instrument from the Bag303.11.2Installation30                           |

|   | 3.12  | 3.11.3           | Installing Instrument Drivers                                    |  |  |

|---|-------|------------------|------------------------------------------------------------------|--|--|

|   | 3.12  | wuiti            | Instrument Synchronization                                       |  |  |

|   |       | 3.12.1           | Master Slave Operation                                           |  |  |

|   |       | 3.12.2<br>3.12.3 | Connecting the Instruments<br>Operating Synchronized Instruments |  |  |

| 4 | Unde  |                  | g the Instrument                                                 |  |  |

|   | 4.1   | -                | -<br>duction                                                     |  |  |

|   | 4.2   | Gener            | ral Description                                                  |  |  |

|   | 4.3   |                  | m Overview                                                       |  |  |

|   | 4.4   |                  | Aodes of Operation                                               |  |  |

|   |       | 4.4.1            | Direct Mode                                                      |  |  |

|   |       | 4.4.2            | DUC Mode                                                         |  |  |

|   |       | 4.4.3            | Streaming Mode                                                   |  |  |

|   | 4.5   | Chanr            | nel Outputs                                                      |  |  |

|   | 4.6   | Chanr            | nel Dependency                                                   |  |  |

|   |       | 4.6.1            | Inter-Part Channel                                               |  |  |

|   |       | 4.6.2            | Dependencies                                                     |  |  |

|   | 4.7   | 4.6.3            | Intra-Part Channel Dependencies<br>ers                           |  |  |

|   | 4.7   | 00               | ion Mode                                                         |  |  |

|   | 4.0   |                  |                                                                  |  |  |

|   |       | 4.8.1<br>4.8.2   | Arbitrary Mode<br>Task Mode                                      |  |  |

|   | 4.9   |                  | ers                                                              |  |  |

|   | 4.10  | Dynar            | mic Segment Control                                              |  |  |

|   | 4.11  | Trans            | ceiver                                                           |  |  |

|   | 4.12  | Stream           | ming                                                             |  |  |

| 5 | Arbit | rary Mod         | le                                                               |  |  |

|   | 5.1   | Introd           | duction                                                          |  |  |

|   | 5.2   | Wave             | form Memory                                                      |  |  |

|   | 5.3   | Chanr            | nel Dependency                                                   |  |  |

|   | 5.4   | Arbitr           | ary Waveform Segments                                            |  |  |

|   | 5.5   | Types            |                                                                  |  |  |

|   | 5.6   | Writir           | ng                                                               |  |  |

|   | 5.7   | Readi            | ng                                                               |  |  |

|   | 5.8   | Stream           | ming                                                             |  |  |

| 6 | Task  | Mode             |                                                                  |  |  |

|   | 6.1   | Introd     | uction                      | 47 |

|---|-------|------------|-----------------------------|----|

|   | 6.2   | Task T     | able                        | 47 |

|   | 6.3   | Task T     | able Parameters             | 49 |

|   | 6.4   | Task T     | able Limitations            | 53 |

|   |       | 6.4.1      | Conditional Jump            | 53 |

|   |       | 6.4.2      | Segment Transitions         | 53 |

|   |       | 6.4.3      | Trigger Signal              | 53 |

|   | 6.5   | Scenai     | io Table                    | 53 |

| 7 | Mark  | (ers       |                             | 54 |

|   | 7.1   | Introd     | uction                      | 54 |

|   | 7.2   | Marke      | r Control                   | 54 |

|   | 7.3   | Progra     | mming the Markers           | 54 |

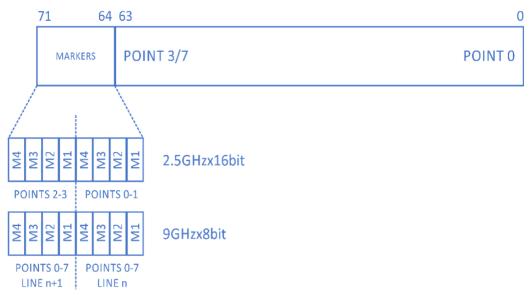

|   |       | 7.3.1      | P9082X Models               |    |

| _ |       | 7.3.2      | All other Models            |    |

| 8 | DUC   | Operation  |                             | 59 |

|   | 8.1   | Introd     | uction                      | 59 |

|   | 8.2   | NCO N      | lode                        | 62 |

|   | 8.3   | ONE N      | 1ode                        | 64 |

|   | 8.4   | TWO        | Node                        | 67 |

|   | 8.5   | HALF       | Mode                        | 68 |

|   | 8.6   | Wavef      | orm Normalization           | 69 |

| 9 | Trigg | ering Syst | em                          | 72 |

|   | 9.1   | Introd     | uction                      | 72 |

|   | 9.2   | Trigge     | r Run Modes                 | 72 |

|   | 9.3   | Arbitra    | ary Mode                    | 72 |

|   | 9.4   | Task N     | 1ode                        | 72 |

|   | 9.5   | Trigge     | r Source                    | 72 |

|   |       | 9.5.1      | TRIG 1/2                    | 73 |

|   |       | 9.5.2      | Bus                         | 73 |

|   |       | 9.5.3      | Abort (Jump) Mode           | 73 |

|   |       | 9.5.4      | Internal Trigger            | 73 |

|   |       | 9.5.5      | Digitizer (AWT)             | 74 |

|   |       | 9.5.6      | Dynamic Jump Connector (DJ) | 74 |

|   | 9.6   | Trigge     | r Source Attributes         | 74 |

|   |       | 9.6.1      | TRIG ½                      | 74 |

|   |       | 9.6.2      | Internal Trigger            | 75 |

|   |       |            |                             |    |

|    | 9.7   | Output Channel Trigger Settings      |

|----|-------|--------------------------------------|

|    |       | 9.7.1 Enable (Start) Source          |

|    |       | 9.7.2 Disable (Abort) Source76       |

|    |       | 9.7.3 Idle Waveform                  |

|    |       | 9.7.4 DC Level                       |

|    |       | 9.7.5 Loops Count                    |

|    | 9.8   | 9.7.6 Low trigger Jitter(LTJ Option) |

| 10 |       | Digitizer                            |

|    | 10.1  | Introduction                         |

|    | 10.2  | Theory of Operation                  |

|    | 10.3  | Working Modes                        |

|    | 10.4  | Acquisition Modes                    |

|    | 10.5  | Trigger Modes                        |

|    | 10.6  | Frame Header                         |

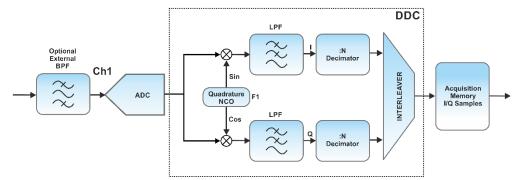

|    | 10.7  | DDC Operation                        |

| 11 |       | Remote Control                       |

|    | 11.1  | Introduction                         |

|    | 11.2  | Wave Design Studio                   |

|    | 11.3  | SCPI Programming                     |

|    | 11.4  | IVI Driver Programming 100           |

| 12 |       | Proteus Module Specifications        |

|    | 12.1  | Channels Characteristics             |

|    | 12.2  | Arbitrary Mode                       |

|    | 12.3  | Task Mode 101                        |

|    | 12.4  | Streaming (STM Option) 102           |

|    | 12.5  | Signal Purity                        |

|    | 12.6  | DC Output 103                        |

|    | 12.7  | Direct Output                        |

|    | 12.8  | Sample Clock Output 104              |

|    | 12.9  | Sync Clock Output                    |

|    | 12.10 |                                      |

|    | 12.11 | Reference Clock Output 105           |

| 14 | Α     | ppendix Log File                                 |

|----|-------|--------------------------------------------------|

| 13 | А     | ppendix A. MDR Interface                         |

|    | 12.26 | Ordering Information Options110                  |

|    | 12.25 | Ordering Information Module 110                  |

|    | 12.24 | Ordering Information Desktop110                  |

|    | 12.23 | Ordering Information Benchtop109                 |

|    | 12.22 | General                                          |

|    | 12.21 | General Module                                   |

|    | 12.20 | General Desktop                                  |

|    | 12.19 | General Benchtop 108                             |

|    | 12.18 | Digital Upconverter                              |

|    | 12.17 | FPGA Programming                                 |

|    | 12.16 | Digitizer Characteristics (AWT Option)106        |

|    | 12.15 | Fast Segment Dynamic Control Input (Optional)106 |

|    | 12.14 | Trigger Inputs                                   |

|    | 12.13 | Sample Clock Input 105                           |

|    | 12.12 | Reference Clock Input 105                        |

# **Figures**

| Figure 2.1 Proteus Model P2584M         | 19 |

|-----------------------------------------|----|

| Figure 2.2 Proteus Model P9484M-AWT     | 20 |

| Figure 2.3 P9802M-AWT                   | 23 |

| Figure 2.4 P2584M Front Panel           | 24 |

| Figure 2.5 P9484M-AWT Front Panel       | 27 |

| Figure 4.1 Proteus Model Numbering      | 33 |

| Figure 4.2 Proteus Block Diagram        | 34 |

| Figure 4.3 NCO Block Diagram            | 35 |

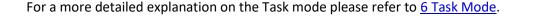

| Figure 4.4 Task Mode                    |    |

| Figure 5.1 Waveform Memory              | 42 |

| Figure 5.2 Waveform Memory Organization | 43 |

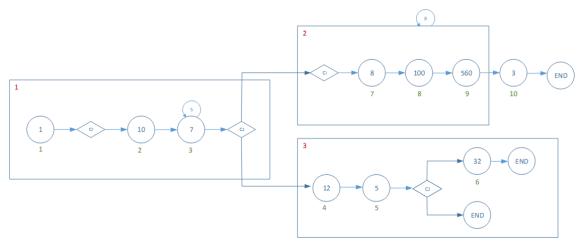

| Figure 6.1 Type of Blocks Implemented by the Task Table                                                                               |

|---------------------------------------------------------------------------------------------------------------------------------------|

| Figure 6.2 Flowchart for an Example Task Table49                                                                                      |

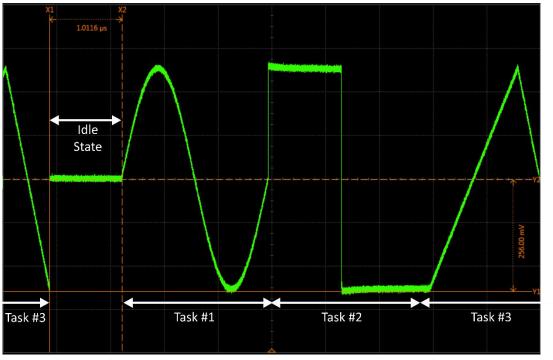

| Figure 6.3 DC Level Idle State Associated to Task #150                                                                                |

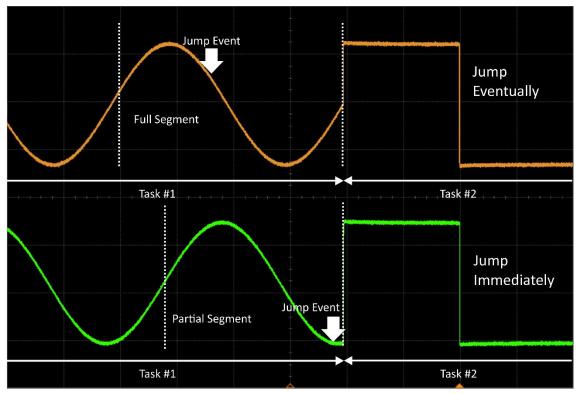

| Figure 6.4 Different types of Jumps. Jump Eventually (Top) and Jump Immediately (Bottom)52                                            |

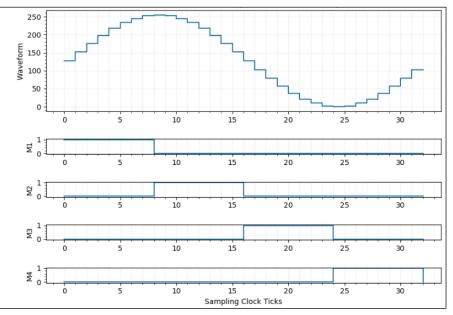

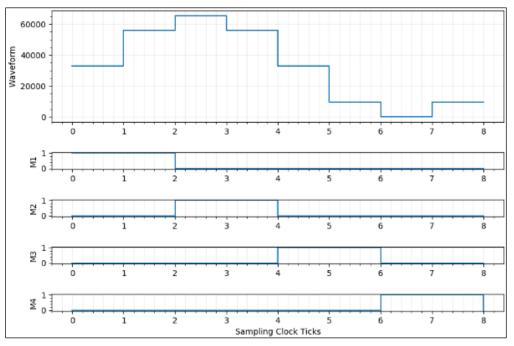

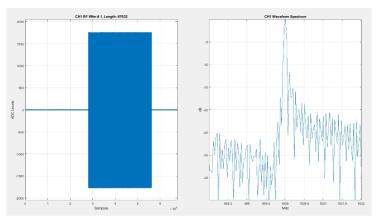

| Figure 7.1 9 GS/s Model - 32 Waveform Points and 4 Marker Points                                                                      |

| Figure 7.2 Segment Data56                                                                                                             |

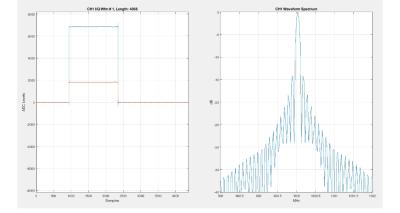

| Figure 7.3 P2582M Model 8 Waveform Points and 4 Marker Points                                                                         |

| Figure 7.4 Segment Data58                                                                                                             |

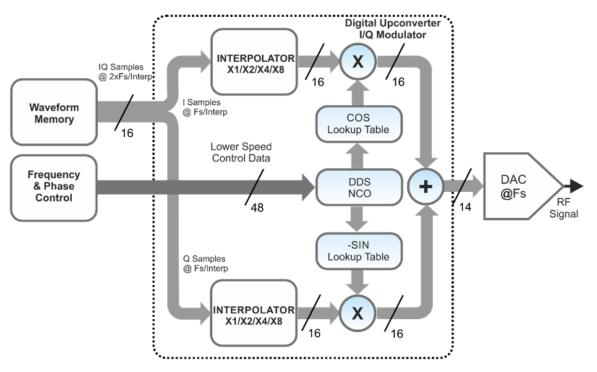

| Figure 8.1 IQ Modulator Block Diagram59                                                                                               |

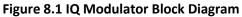

| Figure 8.2 DUC Working Modes for Proteus P948X and P258X61                                                                            |

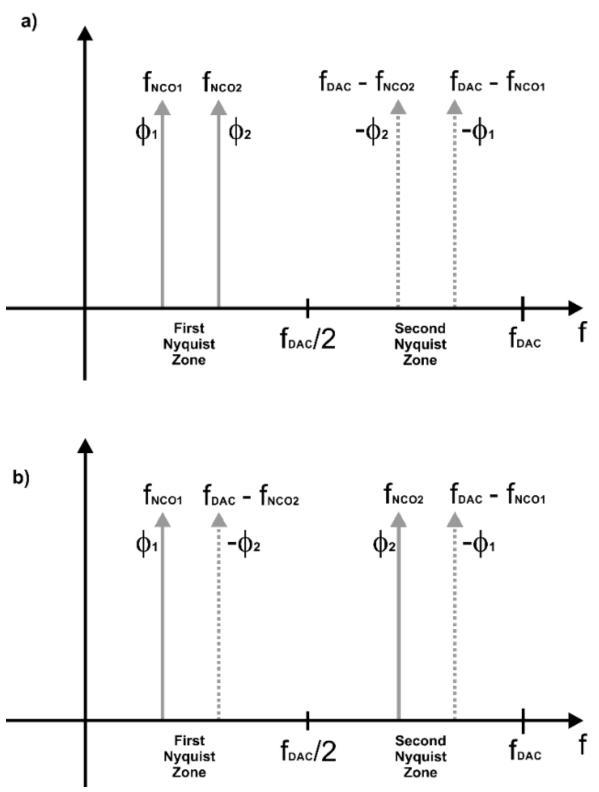

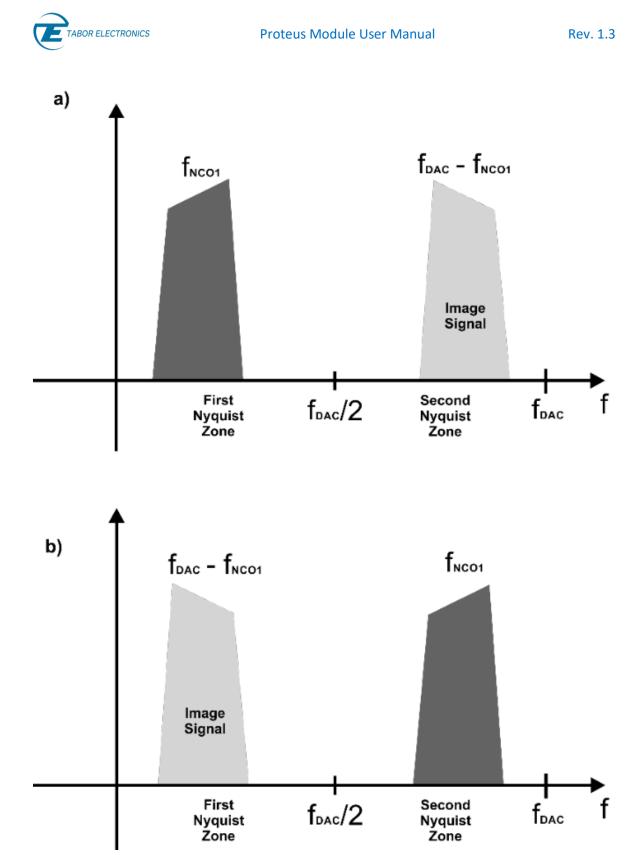

| Figure 8.3 Effects of Setting the NCO Frequency within the First (a) and the Second (b) Nyquist Band63                                |

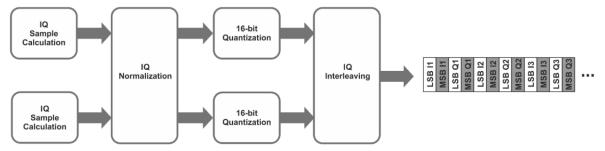

| Figure 8.4 I/Q Sample Processing for Download to the Waveform Memory in Proteus Working in the DUC 'ONE' Mode                         |

| Figure 8.5 I/Q Effects of Setting the NCO Frequency within the First (a) and the Second (b) Nyquist Band for the IQ Modulated Signals |

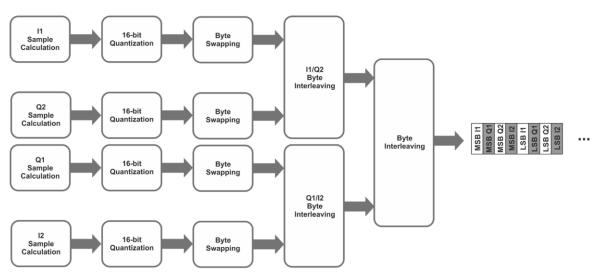

| Figure 8.6 I1/Q1/I2/Q2 Sample Processing for Download to the Waveform Memory in Proteus Working in the DUC 'TWO' mode67               |

| Figure 8.7 Generation of Two Modulated Signals Located in Different Nyquist Bands in the "TWO" Mode                                   |

| Figure 8.8 Alternative Method of Reversion of the Spectrum for the "HALF" Mode                                                        |

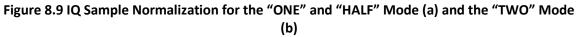

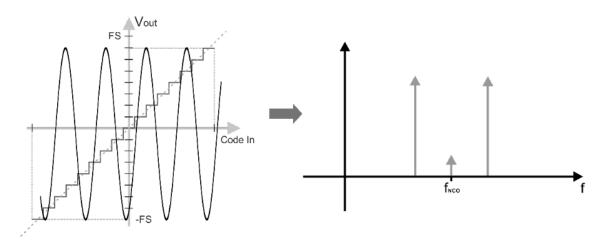

| Figure 8.9 IQ Sample Normalization for the "ONE" and "HALF" Mode (a) and the "TWO" Mode (b)70                                         |

| Figure 8.10 DAC Range Adaption to Avoid the Residual Carrier Impairment in the Output as Seen in (a)71                                |

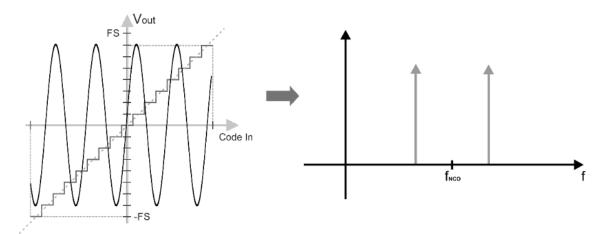

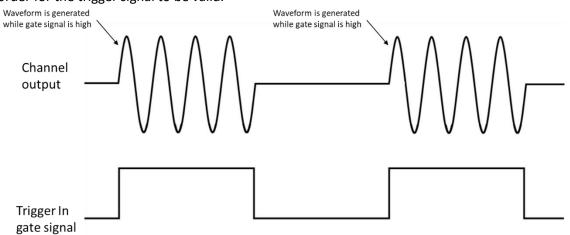

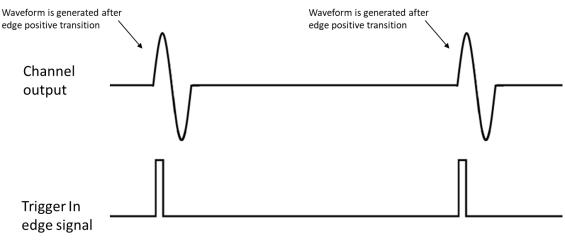

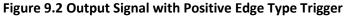

| Figure 9.1 Output Signal with Gate Type Trigger74                                                                                     |

| Figure 9.2 Output Signal with Positive Edge Type Trigger75                                                                            |

| Figure 9.3 Outputs Behavior with Pulse Detect Width Set to Time t <sub>valid</sub> 75                                                 |

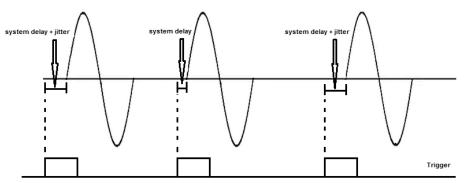

| Figure 9.4 Trigger Jitter and System Delay77                                                                                          |

| Figure 10.1 Digitizer Section Block Diagram for DUAL Mode79                                                                           |

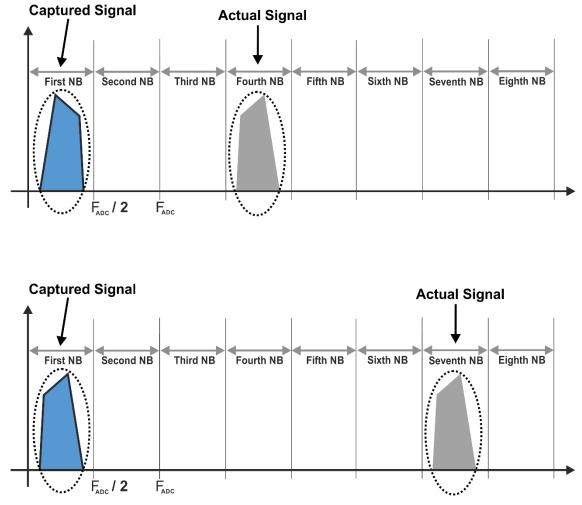

| Figure 10.2 Capturing Signals Beyond 1st Nyquist Band80                                                                               |

| Figure 10.3 Digitizer Section Block Diagram for SINGLE Mode81                                                                         |

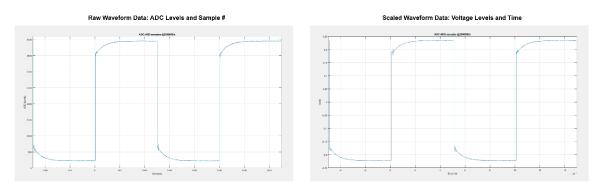

| Figure 10.4 Waveform Before (Left) and After (Right) Proper Voltage and Time Scaling81                                                |

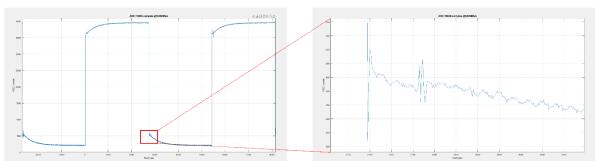

| Figure 10.5 Dual Mode (Two Channels, Half Sample Rate, Top) vs. Single Mode (One Channel, Bottom) Acquisitions                        |

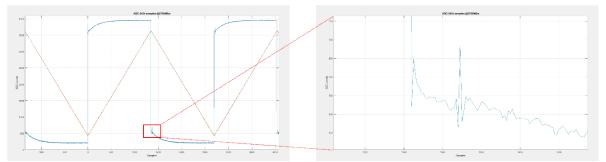

| Figure 10.6 Direct Mode (Top) vs. DDC Mode (Bottom) Acquisitions of an RF pulse and the Corresponding Spectrums                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

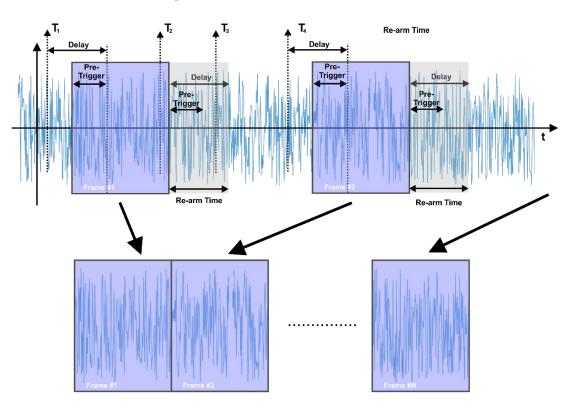

| Figure 10.7 Structure of a Multi-Frame Acquisition84                                                                                                                                                         |

| Figure 10.8 Acquisition Window Control85                                                                                                                                                                     |

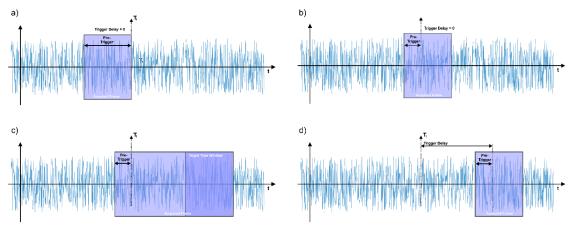

| Figure 10.9 Independent Acquisition86                                                                                                                                                                        |

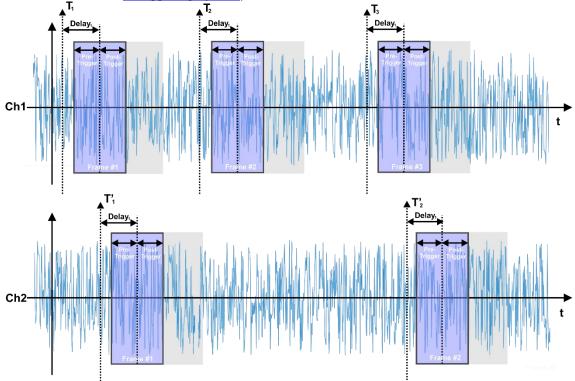

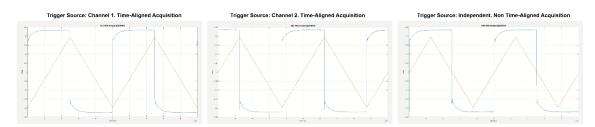

| Figure 10.10 Two-Channel Self-Triggered Acquisitions with Trigger Source from Ch1 (Left), Ch2<br>(Middle), and Independent (Right)87                                                                         |

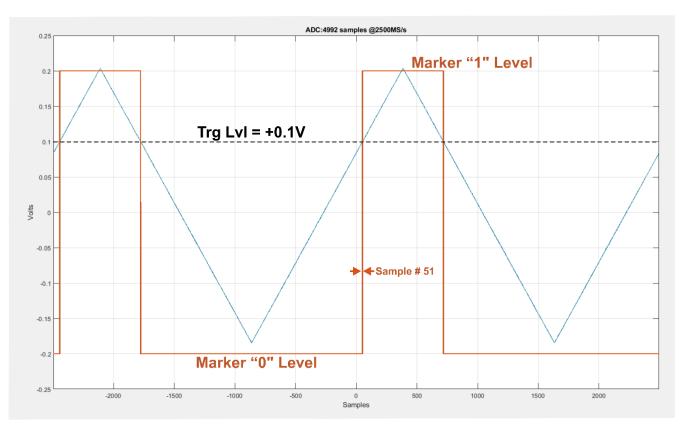

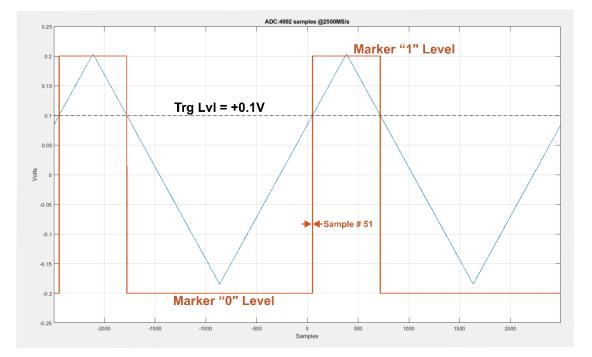

| Figure 10.11 Marker Mode                                                                                                                                                                                     |

| Figure 10.12 Trigger Signal Applied to Ext Trigger Input and Ch1. The Red Trace Shows the<br>Contents of the LSB of the Acquired Waveform in the Marker Mode and the Actual Position of the<br>Trigger Event |

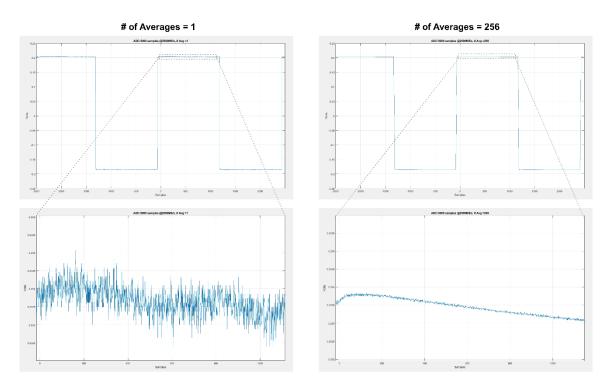

| Figure 10.13 Averaged Acquisitions of Repetitive Waveforms (Right) Results in Lower Noise and<br>Higher Resolution Acquired Waveform Respect to Non-Averaged Waveforms (Left)90                              |

| Figure 10.14 Proteus P9484M-AWT Front Panel91                                                                                                                                                                |

| Figure 10.15 Task Trigger92                                                                                                                                                                                  |

| Figure 10.16 Digital Down-Converter (DDC)94                                                                                                                                                                  |

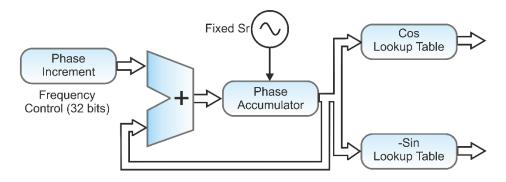

| Figure 10.17 NCO Block Diagram95                                                                                                                                                                             |

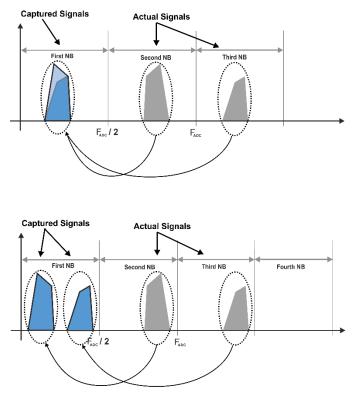

| Figure 10.18 DDC RF Signals Over Multiple NZ96                                                                                                                                                               |

| Figure 11.1 WDS Log Window and Command Editor $\ldots 100$                                                                                                                                                   |

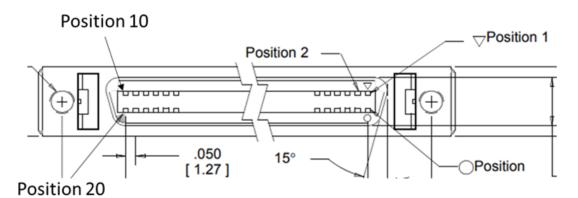

| Figure 13.1 MDR Connector Pin Numbering112                                                                                                                                                                   |

| Figure 13.2 MDR Connector Pad Description112                                                                                                                                                                 |

| Figure 14.1 WDS Log File Folder $\dots 11^4$                                                                                                                                                                 |

| Figure 14.2 WDS Log File                                                                                                                                                                                     |

# **Tables**

| Table 2.1 Ordering Information                                                                    | 18 |

|---------------------------------------------------------------------------------------------------|----|

| Table 2.2 Available Options for Proteus Series Module Platform                                    | 21 |

| Table 2.3 Memory Configuration and Options                                                        | 22 |

| Table 4.1 Proteus Models vs. GS/s                                                                 | 33 |

| Table 4.2 Waveform Sampling Rate Range vs. DAC Sampling Rate as a Function of the Interpol Factor |    |

| Table 7.1 Byte of Marker Data 9 GS/S Models Channel 1/2                                           | 54 |

| Table 7.2 Byte of Marker Data 1.25 GS/S and 2.5 GS/S Models                                       | 56 |

| Table 7.3 Byte of Marker Data 1.25 GS/S and 2.5 GS/S Models                                       | 57 |

| Table 8.1 P948X Maximum DAC and I/Q Sample Rate (SR)6                    | 0 |

|--------------------------------------------------------------------------|---|

| Table 10.1 First 5 Frame Header Fields                                   | 3 |

| Table 12.1 Channels Characteristics Specifications         10            | 1 |

| Table 12.2 Arbitrary Mode Specifications       10                        | 1 |

| Table 12.3 Task Mode Specifications    10                                | 1 |

| Table 12.4 Streaming (STM Option) Specifications                         | 2 |

| Table 12.5 Signal Purity Specifications         10                       | 2 |

| Table 12.6 DC Output Specifications    10                                | 3 |

| Table 12.7 Direct Output Specifications       10                         | 3 |

| Table 12.8 Sample Clock Output Specifications       10                   | 4 |

| Table 12.9 Sync Clock Output Specifications         10                   | 4 |

| Table 12.10 Marker Outputs Specifications         10                     | 4 |

| Table 12.11 Reference Clock Output Specifications         10             | 5 |

| Table 12.12 Reference Clock Input Specifications         10              | 5 |

| Table 12.13 Sample Clock Input Specifications10                          |   |

| Table 12.14 Trigger Inputs Specifications         10                     | 6 |

| Table 12.15 Fast Segment Dynamic Control Input (Optional) Specifications | 6 |

| Table 12.16 Digitizer Characteristics (AWT Option) Specifications        | 6 |

| Table 12.17 FPGA Programming Specifications         10                   | 7 |

| Table 12.18 Digital Upconverter Specifications         10                | 7 |

| Table 12.19 General Benchtop Specifications       10                     | 8 |

| Table 12.20 General Desktop Specifications       10                      | 8 |

| Table 12.21 General Module Specifications       10                       | 9 |

| Table 12.22 General Specifications    10                                 | 9 |

| Table 12.23 Ordering Information Benchtop       10                       | 9 |

| Table 12.24 Ordering Information Desktop       11                        | 0 |

| Table 12.25 Ordering Information Module       11                         | 0 |

| Table 12.26 Ordering Information Options11                               | 0 |

| Table 13.1 MDR Connector Pin Description                                 | 2 |

# **1** General

#### 1.1 Scope

The scope of this manual is to describe the setup and operating procedures of the Tabor Electronics Proteus series module platform.

### **1.2 Related Documentation**

- Wave Design Studio User Manual

- Proteus Programming Manual

- Proteus Series Performance Verification Manual

- Proteus DUC Primer

- Proteus AWT Radar Primer

- Qubit Characterization (IEEE Applications Note)

- Direct Generation/Acquisition of Microwave Signals

- Effective Number of Bits for Arbitrary Waveform Generators

# **1.3 Software Support**

The **Wave Design Studio (WDS)** is a software package that enables full control and programming of your Tabor Electronics device via a user-friendly graphical user interface. Use the **TE Update Tool** to update the Proteus device FPGA. The programs and the user manual can be downloaded from the Tabor Electronics website at <a href="http://www.taborelec.com/downloads">http://www.taborelec.com/downloads</a>.

# **1.4 Document Conventions**

### 1.4.1 General

| Convention                                        | Description                                      | Example                      |

|---------------------------------------------------|--------------------------------------------------|------------------------------|

| Bold Writing                                      | Indicates an item/message in the User Interface. | Click the <b>On</b> button.  |

| <angled and="" bolded<br="">Brackets&gt;</angled> | Indicates a physical key on the keyboard.        | Press <ctrl>+<b>.</b></ctrl> |

#### **Caution!**

A Caution indicates instructions, which, if not followed, may result in damage to the equipment or to the loss of data.

Note

A note provides additional **information** to help obtain optimal equipment performance.

Idea

An idea provides an alternate procedure to obtain the same results.

### 1.5 Safety

To avoid electrical shock, fire or personal injury:

- Use only the proper power cord and certified for the country of use.

- This product is grounded through the grounding conductor of the power cord. To avoid electrical shock, the grounding conductor must be connected to the ground. Before connecting to the power input or output, ensure that the product is properly grounded.

- Do not operate this product with removed covers or panels.

- Observe all the ratings and markings on the product. Search this manual for further rating information, before connecting to it. Do not apply potential that is higher than the maximum rating.

- Do not operate in dark or wet conditions.

- Do not operate in an explosive environment. Keep product clean and dry.

#### 1.6 Maintenance

#### **1.6.1 Preventive Maintenance**

There are no hardware adjustments within Proteus Generators. Tabor Electronics Ltd., recommends that the Proteus Generator is calibrated every 24 months or whenever a problem is suspected. The specific calibration interval depends upon the accuracy required. No periodic preventive maintenance is required.

#### **1.6.2** Long Term Storage or Repackaging For Shipment

If the instrument is to be stored for a long period of time or shipped immediately, proceed as directed below. If you have any questions, contact your local Tabor Electronics representative or the Tabor Electronics Customer Service Department.

- 1. Repack the instrument using the wrappings, packing material and accessories originally shipped with the unit. If the original container is not available, purchase replacement materials.

- 2. Be sure the carton is well sealed with strong tape or metal straps.

- 3. Mark the carton with the model and serial number. If it is to be shipped, show sending and return address on two sides of the box.

- 4. If the instrument is to be shipped for service or repair, the following information must be included with the shipment:

- Name and address of the owner.

- Record the model and serial number of the instrument, options, and firmware version.

- Note the problem and symptoms detailed information will help in verifying the problem

- What was the instrument setup, such as the run mode, arbitrary/task mode, task table etc.

- Did the unit work; then fail or was it dead on arrival.

- What other equipment was connected to the generator when the problem occurred, such as external trigger or clock.

- The name and telephone number of someone familiar with the problem who can be contacted by Tabor Electronics if any further information is required.

- Show the returned authorization order number (RMA) as well as the date and method of shipment.

#### Note

Always obtain a return authorization number from the factory before shipping the instrument to Tabor Electronics.

# **2** Introduction

### 2.1 **Overview**

This manual provides a detailed functional description for the Tabor Electronics Proteus series module platform. Proteus is a series of arbitrary waveform generators and transceivers that transmit, receive and perform digital signal processing all in a single instrument with various form-factors and sampling rate options. The Proteus module is PXIe-based (PCI Express eXtension for Instrumentation) to be plugged into a standard PXIe chassis such as the Tabor PXE21100, 21 slot PXIe chassis. The manual covers the following models listed in the below ordering information. For a list of options refer to Table 2.2 Available Options for Proteus Series Module Platform.

| Model  | Description                                                             |

|--------|-------------------------------------------------------------------------|

| P1282M | 1.25 GS/s, 16 bit, 1 GS memory, 2 channels, 4 markers, module RF<br>AWG |

| P1284M | 1.25 GS/s, 16 bit, 1 GS memory, 4 channels, 4 markers, module RF<br>AWG |

| P2582M | 2.5 GS/s, 16 bit, 2 GS memory, 2 channels, 8 markers, module RF<br>AWG  |

| P2584M | 2.5 GS/s, 16 bit, 2 GS memory, 4 channels, 8 markers, module RF<br>AWG  |

| P9082M | 9 GS/s, 8 bit, 4 GS memory, 2 channels, 8 markers, module RF<br>AWG     |

| P9482M | 9 GS/s, 16 bit, 8 GS memory, 2 channels, 8 markers, module RF<br>AWG    |

| P9484M | 9 GS/s, 16 bit, 8 GS memory, 4 channels, 8 markers, module RF<br>AWG    |

| Table 2. | 1 Ordering | Information |

|----------|------------|-------------|

|----------|------------|-------------|

Note

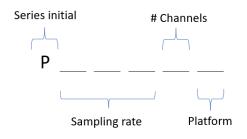

**P2582M** = **P** (Model = Proteus) + **258** (Sampling Rate = 25E08 = 2.5E9) + **2** (# channels = 2) + **M** (Platform = Module)

Figure 2.1 Proteus Model P2584M

Figure 2.2 Proteus Model P9484M-AWT

# 2.2 Features and Highlights

- Dual or four channel 1.25 GS/s & 2.5 GS/s, 16-bit, or dual channel 9 GS/s, 8-bit, AWG & AWT (Arbitrary Waveform Generator/Transceiver) configurations

- Four channels 9GS/s 16 bit, AWG & AWT configurations (P9482M, P9484M).

- Integrated NCO (Numerically Controlled Oscillator) for digital upconverting to microwave frequencies

- Real time data streaming directly to the FPGA for continuous and infinite waveform generation

- 8 GHz bandwidth, 5.4 GS/s 12-bit digitizer option for feedback control system and conditional waveform generation

- Innovative task-oriented sequence programming for maximum flexibility to generate any imaginable scenario

- Up to 16 GS waveform memory with the ability to simultaneously generate and download waveforms

- Excellent phase noise and spurious performance

- User customizable FPGA block for real time processing and application specific functionality

- High speed PCIe GEN3 x8 lanes communication interface

• Modular and space efficient PXIe (PCI Express eXtension for Instrumentation) platform, easily scalable to hundreds of channels

# 2.3 System Requirements

The following is required to operate Proteus:

- PXIe compatible chassis

- PC with Windows 10 operating system

# 2.4 **Options**

The Proteus series module platform is a dual-slot PXIe arbitrary waveform generator and can be ordered with the following options.

| Option | Description                                            | Model                             |

|--------|--------------------------------------------------------|-----------------------------------|

| 4M1    | 4 GS memory                                            | P1282M, P2582M                    |

| 4M2    | 4 GS memory                                            | P1284M, P2584M                    |

| 8M1    | 8 GS memory                                            | P1282M, P2582M                    |

| 8M2    | 8 GS memory                                            | P1284M, P2584M, P9082M            |

| 16M1   | 16 GS memory                                           | P9082M                            |

| DO1    | 9 GHz BW direct (DAC) output                           | P1282M, P2582M                    |

| DO2    | 9 GHz BW direct (DAC) output                           | P1284M, P2584M, P9082M            |

| DC1    | DC output for IQ baseband applications                 | P9482M                            |

| DC2    | DC output for IQ baseband applications                 | P9484M                            |

| DJ1    | Dynamic jump input option, occupies an additional slot | P1282M, P2582M, P9482M            |

| DJ2    | Dynamic jump input option, occupies an additional slot | P1284M, P2584M, P9082M,<br>P9484M |

| LVTTL1 | LVTTL marker output                                    | P128xM, P258xM, P9082M,<br>P948xM |

| MRK1   | 4 extra markers, occupies an additional slot           | P1282M, P2582M, P9482M            |

| MRK2   | 8 extra markers, occupies an additional slot           | P1284M, P2584M, P9082M,<br>P9484M |

| LTJ1   | Ultra-low trigger jitter                               | P1282M, P2582M, P9482M            |

| LTJ2   | Ultra-low trigger jitter                               | P1284M, P2584M, P9082M,<br>P9484M |

| G1     | Low waveform granularity                               | P1282M, P2582M, P9482M            |

#### Table 2.2 Available Options for Proteus Series Module Platform

| G2       | Low waveform granularity                                                             | P1284M, P2584M, P9082M,<br>P9484M |

|----------|--------------------------------------------------------------------------------------|-----------------------------------|

| DUC      | Digital up-converter for models                                                      | P2582M, P2584M                    |

| TRG      | Faster trigger input (50 MHz instead of 10 MHz)                                      | All models                        |

| AWT      | 5.4 GS/s single, 2.7 GS/s dual channel 12-bit digitizer, occupies an additional slot | All models                        |

| STM      | Up to 6 GS/s streaming option depending on model                                     | All models                        |

| PROG     | FPGA programming capability with built-in demodulation and digital filters           | All models                        |

| Shell    | Integration to allow simple FPGA control and programming                             | All models                        |

| PXE21100 | 21 slot PXIe chassis                                                                 | All models                        |

| PXE6410  | 6 slot PXIe chassis with an embedded PC                                              | All modules                       |

**Option M** – This option offers to increase the standard waveform memory of the unit as detailed in the table below:

| Model  | Standard | 4M1 | 4M2 | 8M1 | *8M2 | 16M1 |

|--------|----------|-----|-----|-----|------|------|

| P1282M | 1GS      | 4GS |     | 8GS |      |      |

| P1284M | 1GS      |     | 4GS |     | 8GS  |      |

| P2582M | 2GS      | 4GS |     | 8GS |      |      |

| P2584M | 2GS      |     | 4GS |     | 8GS  |      |

| P9082M | 4GS      |     |     |     | 8GS  | 16GS |

#### Table 2.3 Memory Configuration and Options

**Option DO** – There are two available output configurations:

- Direct Output (DO): This is a direct AC coupled output without an amplifier and is optimized for maximum analog BW as well as best SFDR (Spurious Free Dynamic Range). It offers a programmable amplitude range of 1mVpp to 550 mVpp.

- 2. DC Output: This is the default configuration. A DC coupled output amplifier offering up to 1.3 Vpp with a voltage window of ±1.15 V.

#### Note

The P948xM comes with DO as default.

**Option DJ** – This option offers the capability of switching segments through an external MDR connector. The MDR connector occupies an additional PXI slot. Refer to <u>13 Appendix A. MDR</u> <u>Interface</u> for a pin description.

**Option MRK** – This option adds a digital markers card, with 8 additional markers and occupies an extra PXI slot.

**Option LVTTL** – This option LVTTL marker output (replaces the 1.3Vpp default markers).

**Option LTJ** – This option improves the Proteus trigger jitter to SQRT(SCLK period^2 + 150e-12^2).

Rev. 1.3

**Option G** – This option increases the segment resolution for segments that are both fast and short. In the case of the P9082M the segment resolution, for the first 128 segments that are shorter than 8kpts, is increased to 32 points. For the P128xM, P258xM and P948XM, the segment resolution, for the first 128 segments that are shorter than 4kpts, is increased to 16 points.

**Option AWT** – This option transforms the Proteus to an arbitrary waveform transceiver with the capability of both generating and receiving signals. The option adds a 2.7 GS/s dual channel or 5.4 GS/s single channel digitizer card allowing to complete a fully closed loop system controlled by a single FPGA. With this option the Proteus AWT occupies 3 PXIe slots.

**Option PROG** – This option enables the user to use built in digital processing library blocks such as demodulators, filters and math functions as part of the signal processing chain without FPGA programming knowledge.

**Option Shell** – This option is for users with advanced FPGA programming knowledge in Xilinx Vivado Design Suite. The Proteus is supplied only with the necessary communications and data transfer cores and enables the user to implement their own IP on the available resources of the FPGA. The options depicted below require an additional PXIe slot.

Figure 2.3 P9802M-AWT

#### 2.5 Front Panel

The front panel of the Proteus device varies according to the device model and configuration. However, regardless of the configuration, all connector types follow the same principle. All high-frequency analog output and input connectors are of SMA type. All low-frequency analog output

and input connectors as well as all digital output and input connectors are of SMP type. In addition, there is a "STATE" LED to indicate if there is any problem with the device. Below is the front panel of the P2584M model:

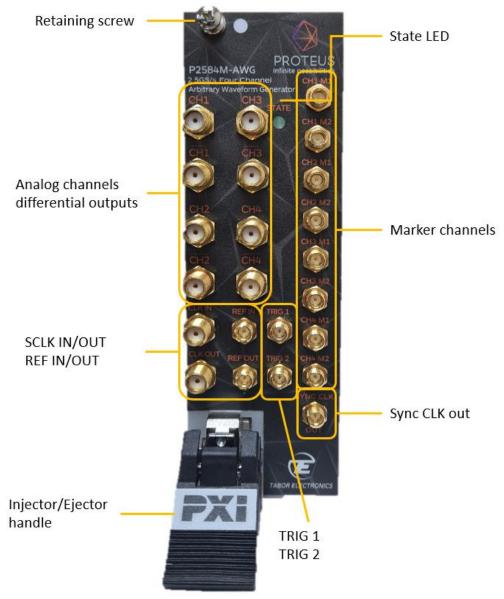

Figure 2.4 P2584M Front Panel

- Retaining Screw The retaining screw is used to secure the module to the PXIe chassis.

- CH1/2/3/4 There are two SMA connectors for each channel output, normal (top) and inverted (bottom) outputs. The output source impedance is 50 Ω (100 Ω when connected differentially) therefore the cable connected to this output should be terminated with a 50 Ω load resistance. For different load resistance, determine the actual amplitude from the following equation:

$$V_{out} = 2V_{prog} \left(\frac{R_{load}}{50 + R_{load}}\right)$$

The output amplitude is doubled when the load impedance is above roughly 10 k $\Omega$ . Also, the output can be turned on and off. However, turning the output off stops the signal, but leaves low impedance on the output terminals.

#### Note

When using the outputs as single ended it is necessary to use a 50  $\Omega$  termination on the inverted output to prevent any distortion on the output signal.

- CLK IN The sample clock in SMA connector accepts an external signal that will replace the internal sample clock generator. This input, accepts signals covering the instrument's entire sample clock range, with an input level range of 0 V to 1 V. The output impedance of this connector is 50 Ω and it is AC coupled. The sample clock input is active only after selecting the external SCLK source option.

- CLK OUT The sample clock out SMA connector outputs the internal sample clock generator or the external SCLK if an external sample clock is used. The sample clock out signal covers the entire sample clock range, with an output amplitude of 0.5 V to 1 V depending on the frequency. The output impedance of this connector is 50 Ω and it is AC coupled.

- **REF IN** The reference in SMP connector accepts signals of either 10 MHz or 100 MHz. This input is normally used for synchronizing system components to a single clock reference. The Proteus device must be programmed to the reference frequency value and placed in external reference mode before it will use this input as reference.

- REF OUT The reference out SMP connector outputs the 100M Hz internal reference (square waveform) or if using an external reference, the Ref Out outputs the external reference frequency. This output can be used to synchronize other system components to the Proteus clock reference.

#### **Module Synchronization**

When synchronizing multiple modules, the modules need to be daisy chained between REF OUT to REF IN. Therefore, in this mode the REF OUT is not available and is used for synchronization. The REF IN of the master unit can accept an external reference signal, and this will be the reference for all modules.

- **STATE** System status LED.

- Solid Green Normal operation.

- Off System fault. Contact Tabor Electronics.

- TRIG 1/2 In general, the trigger inputs are used to initiate or abort waveform generation. In arbitrary mode this is used to start or stop a current segment from playing. In task mode this can also be used as a condition signal for how to progress in the task table. The trigger input is inactive when the generator is in continuous operating mode. When placed in trigger mode, the trigger input is made active and waits for the right condition to trigger the instrument. Trigger level and edge rising/falling edge are programmable for the trigger input. For example, if your trigger signal rides on a DC level, you can offset the trigger level to the same level as your trigger signal, thus assuring the correct threshold for the trigger signal. The trigger level is adjustable from -5 V to +5 V. The programmed trigger level is common for all channels. All other trigger parameters including trigger state, are independent and can be programmed per channel. The two trigger input connectors are of SMP type. By default, the input impedance is 50  $\Omega$  but can be factory configured to 10 k $\Omega$  when ordered.

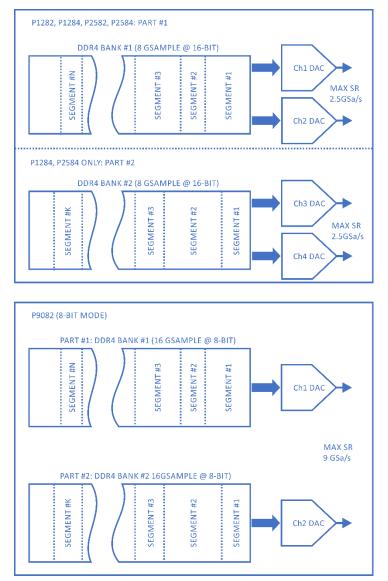

- CH1-4 M1/2 There are between 1 to 4 output markers available for each analog channel output depending on the Proteus model. The markers are generated through SMP connectors and are marked with the channel number they are associated to, and the marker number e.g. CH1 M1 is Marker 1 of Channel 1. Markers can be programmed from remote to create complex digital patterns. Waveform data and marker data are downloaded separately; however each waveform segment has a dedicated marker segment of equal length. Markers output has an output impedance of 50 Ω and marker level can be programmed up to 1.2 Vpp.

- SYNC CLK This SMP connector outputs a clock signal, that is a division of the device sampling clock. For the 9 GS/s Proteus models the sampling clock is divided by 32 and for all other models it is divided by 8. When this signal is used as the sampling clock for an external triggering unit the resulting trigger jitter of the Proteus device will be ~0 ps.

#### 2.5.1 Proteus AWT Front Panel

The front panel of the Proteus AWT (Arbitrary Waveform Transceiver) module occupies three PXIe slots and provides some additional connectors.

Figure 2.5 P9484M-AWT Front Panel

- **CH1/2 IN** The analog input for the digitizer. There is one SMA connector for each channel input. The input load impedance is 50 Ω.

- SCLK IN The external sample clock for the digitizer. The sample clock in SMA connector accepts an external signal that will replace the internal sample clock generator. This input, accepts signals covering the instrument's entire sample clock range, with an input level range of 0 V to 1 V. The output impedance of this connector is 50 Ω and it is AC coupled. The sample clock input is active only after selecting the external SCLK source option.

- **TRIG IN** The trigger input is used to initiate the digitizer acquisition. Trigger level and edge rising/falling edge are programmable for the trigger input. For example, if your trigger signal rides on a DC level, you can offset the trigger level to the same level as your trigger signal, thus assuring the correct threshold for the trigger signal. The trigger level is adjustable from -5 V to +5 V. The programmed trigger level is common for all channels. All other trigger parameters including trigger state, are independent and can be programmed per channel. The trigger input connector is of SMA type. By default, the input impedance is 50  $\Omega$  but can be factory configured to 10 k $\Omega$  when ordered.

- **GPIO1/2** For future use.

# **3** Installation

# 3.1 Installation Overview

This chapter contains information and instructions necessary to prepare the Proteus device for operation. Details are provided for initial inspection, grounding safety requirements, repackaging instructions for storage or shipment and installation information.

# 3.2 Unpacking and Initial Inspection

Unpacking and handling of the device requires normal precautions and procedures applicable to handling of sensitive electronic equipment. The contents of all shipping containers should be checked for included accessories and certified against the packing slip to determine that the shipment is complete.

# **3.3 Safety Precautions**

The following safety precautions should be observed before using this product and associated PXIe chassis. Although some instruments and accessories would normally be used with nonhazardous voltages, there are situations where hazardous conditions may be present. This product is intended for use by qualified persons who recognize shock hazards and are familiar with the safety precautions required to avoid possible injury. The following sections contain information and cautions that must be observed to keep the device operating in a correct and safe condition.

#### **A** Caution

For maximum safety, do not touch the product, test cables, or any other instrument parts while power is applied to the circuit under test. ALWAYS remove power from the entire test system before connecting cables or jumpers, installing or removing cards from the chassis. Do not touch any object that could provide a current path to the common side of the circuit under test or power line (earth) ground. Always keep your hands dry while handling the instrument.

# 3.4 **Operating Environment**

This device is intended for operation within a PXIe chassis as a plug-in module. Ensure the PXIe chassis being used to host the device fully conforms to the latest PXIe specifications, including 3.3 V and 12 V supply rails.

The device is intended for indoor use and should be operated in a clean, dry environment with an ambient temperature within the range of 0°C to 40°C.

#### \rm Warning

The Proteus device must not be operated in explosive, dusty, or wet atmospheres. Avoid installation of the module close to strong magnetic fields

The design of the device has been verified to conform to EN 61010-1 safety standard per the following limits: Installation (Overvoltage) Category I (Measuring terminals) Pollution Degree 2 Installation (Overvoltage) Category I refers to signal level, which is applicable for equipment

measuring terminals that are connected to source circuits in which measures are taken to limit transient voltages to an appropriately low level. Pollution Degree 2 refers to an operating environment where normally only dry non-conductive pollution occurs. Occasionally a temporary conductivity caused by condensation must be expected.

# 3.5 **Performance Checks**

The device has been inspected for mechanical and electrical performance before shipment from the factory. It is free of physical defects and in perfect electrical order. Check the instrument for possible damage in transit and perform the electrical procedures outlined in the section entitled Unpacking and Initial Inspection.

#### **3.6 Power Requirements**

The Proteus device operates in a PXIe chassis. DC voltages are supplied to the instrument from the PXIe connector. The instrument requires 3.3 V and 12 V DC voltages. Ensure the PXIe bus is capable of delivering required voltages and has sufficient current to drive the generator. For current consumption refer to Table 12.1.

#### **L** Caution

Disconnect power to the PXIe chassis before installing or removing the device.

### 3.7 Grounding Requirements

To conform to the applicable safety and EMC requirements, ensure that the Proteus device panel and the PXIe chassis are "earth" grounded.

#### \rm Caution

The outer shells of the front panel terminals are connected to the instrument's chassis and therefore to the safety ground.

Do not attempt to float the OUTPUT from ground as it may damage the device and other equipment connected to the I/O connectors.

# 3.8 Calibration

The recommended calibration interval is one year. Calibration should be performed by qualified personnel only.

#### 3.9 Abnormal Conditions

Operate the device only as intended by the manufacturer. If you suspect the device has been impaired, remove it from the PXIe chassis and secure against any unintended operation. The device protection is likely to be impaired if, for example, the instrument fails to perform the intended measurements or shows visible damage.

#### \rm Warning

Any use of the device in a manner not specified by the manufacturer may impair the protection provided by the instrument

# 3.10 Long Term Storage or Repackaging for Shipment

If the instrument is to be stored for a long period of time or shipped immediately, proceed as directed below. If you have any questions, contact your local Tabor Electronics representative or the Tabor Electronics Customer Service Department.

- 1. Repack the instrument using the wrappings, packing material and accessories originally shipped with the unit. If the original container is not available, purchase replacement materials.

- 2. Be sure the carton is well sealed with strong tape or metal straps.

- 3. Mark the carton with the model and serial number. If it is to be shipped, show sending and return address on two sides of the box.

#### Note

If the instrument is to be shipped to Tabor Electronics for calibration or repair, attach a tag to the instrument identifying the owner. Note the problem, symptoms, and service or repair desired. Record the model and serial number of the instrument. Show the returned material authorization (RMA) order number as well as the date and method of shipment. Always obtain a RMA number from the factory before shipping the instrument to Tabor Electronics.

### 3.11 **Preparation for Use**

Preparation for use include removing the instrument from the bag, installing the device inside the PXIe chassis, and installing instrument drivers on the control computer. Tabor offers a dedicated software, Wave Design Studio, to manage the device.

#### **3.11.1** Removing the Instrument from the Bag

The Proteus device is supplied in an antistatic bag. Check the seal on the bag to make sure the bag was not opened in a static-unsafe environment. Place the enveloped card on static free surface and hook yourself up with a grounding strap. Only then break the seal and remove the card from the envelope. Hold the card at the metal panel end. Refrain from touching the instrument with your finger at all times.

#### 3.11.2 Installation

To install the Proteus Module in a PXIe chassis, follow the steps below:

- 1. Power off and unplug the PXI Express chassis.

- 2. Identify two (or more depending on the options) available and supported PXI Express slots.

- 3. Touch any metal part of the chassis to discharge static electricity.

- 4. Place card edges in the dedicated rails at the top and bottom of the chassis and carefully slide the module to the rear of the chassis.

- 5. When you begin to feel resistance pull up the injector/ejector handle to latch the module.

6. Make sure the metal panel makes contact with the metal edge of the PXIe chassis. Use a suitable screwdriver to tighten the retaining screw to secure the module.

#### \rm Warning

Once the device is installed in the chassis cover all remaining open slots to ensure proper airflow. Using the device without proper airflow will result in damage to the instrument. It is also recommended to use the highest fan setting available on the chassis to ensure proper cooling of the Proteus device.

#### **3.11.3 Installing Instrument Drivers**

The programs, drivers and the user manuals can be downloaded from the Tabor Electronics website at <u>http://www.taborelec.com/downloads</u>. Follow the instructions below to install all the necessary drivers and DLLs on your PC to communicate and control you Proteus device.

The following installation instructions assume that the PXI Express chassis is properly installed and recognized by the controlling PC.

#### Note

Check the Tabor Electronics website for the most recent software, driver, firmware and documentation updates. <u>www.taborelec.com/downloads</u>.

# 3.12 Multi Instrument Synchronization

There are applications that require more than the 2 or 4 channels that a single Proteus module can offer. This is where the scalability of the Proteus PXI Express platform can be utilized. Multiple modules can be synchronized within a single PXI Express chassis to create a multi-channel system. The procedure is described in the following paragraphs.

#### **3.12.1** Master Slave Operation

When synchronizing multiple modules, one is designated as the master and the rest as slaves. The master module provides the system clocks and necessary triggers to synchronize and align all of the modules.

The master module must be placed at the left most or lowest numbered available slot in the chassis. Once the master module is inserted, the next slave module must be inserted in the next available adjacent slot and so on until all modules have been placed.

#### \rm Important

All Proteus modules must be adjacent to one another. There can be no empty slot nor any third-party instruments between Proteus modules.

#### **3.12.2** Connecting the Instruments

Once all the modules have been inserted into the chassis one next to the other, they now need to be cross connected with the designated SMP to SMP synchronization cable. Locate the REF OUT connector of the master instrument (left most module) and attach one end of the cable. Next, connect the other end of the cable to the REF IN connector of the adjacent slave 1 module. Continue

daisy chaining from slave 1 REF OUT to slave 2 REF IN and so on until all modules have been connected.

# **3.12.3** Operating Synchronized Instruments

When operating two or more synchronized instruments, there are some important limitations to be familiar with in order to achieve optimal performance.

- 1. Instruments and cables must be placed and connected as described in previous paragraphs.

- 2. Synchronization mode must be activated either from Wave Design Studio or by SCPI command.

- 3. Synchronization and channels alignment is automatic.

- 4. Manual alignment can be performed to improve the skew between channels.

- 5. Sample clock change is implemented in the master unit alone. Any SCLK change command to one of the slave units will automatically result in the unit exiting from the synchronization mode.

- 6. Other than SCLK change, each instrument can be independently programmed with a unique set of waveforms, segment table, task table, amplitude, offset and markers.

# **4** Understanding the Instrument

# 4.1 Introduction

This section provides a description of the features and functions available in the Proteus module series of arbitrary waveform generators/transceivers.

# 4.2 General Description

The Proteus module series is a dual- or quad-channel arbitrary waveform generator and transceiver. It is designed to offer outstanding performance with new and advanced capabilities and all this in a compact, modular and easily scalable PXIe platform. Incorporating the most advanced and cutting-edge technology ensures that the Proteus series, is and will be for many years to come, the ideal signal source for many applications.

The module platform offers five different models depending on the SCLK speed and number of channels. The model numbering scheme for the Proteus series, except the P948xM, is shown in the figure below:

Figure 4.1 Proteus Model Numbering

#### Example

Model P2582M is a Proteus series model, with a  $25 \times 10^8$  samples per second (2.5 GS/s) sampling rate and 2 output channels based on the Module platform.

The following table summarizes the available Proteus modules.

| Sample Rate<br>Channel Count | 1.25 GS/s | 2.5 GS/s | 9 GS/s         |

|------------------------------|-----------|----------|----------------|

| Dual Channel                 | P1282M    | P2582M   | P9082M, P9482M |

| Quad Channel                 | P1284M    | P2584M   | P9484M         |

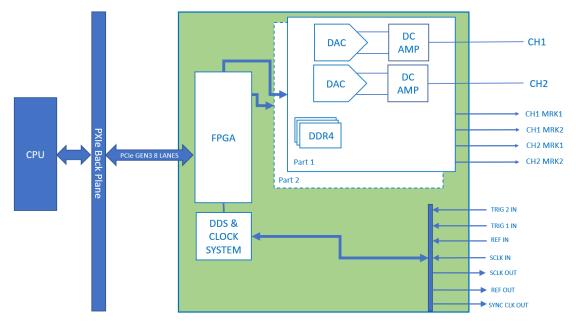

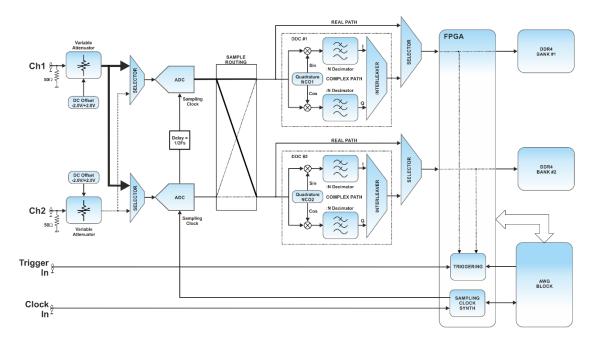

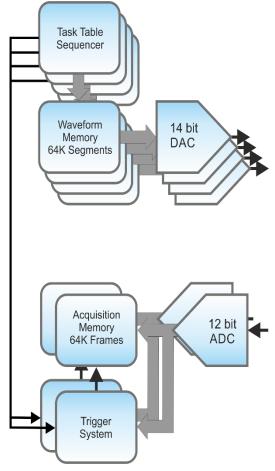

### 4.3 System Overview

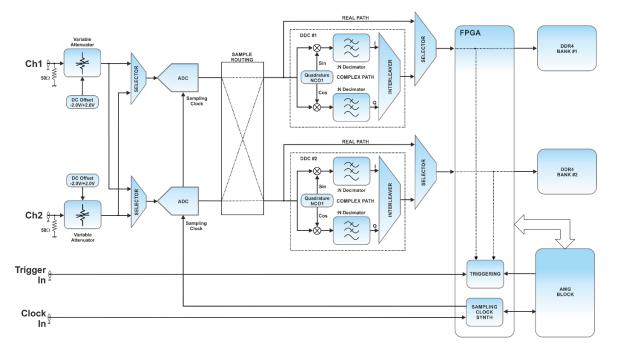

The block diagram below depicts the core of the system without the options.

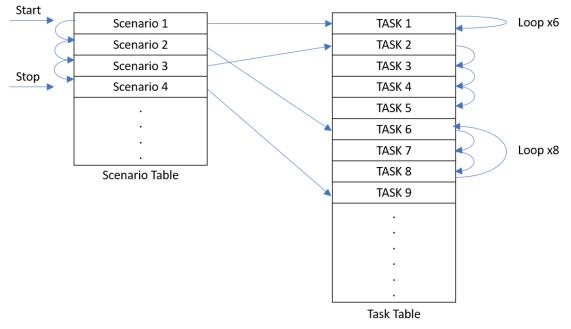

The Proteus system is an AWG (Arbitrary Waveform Generators) module, occupying 2 PXIe (PCI Express eXtension for Instrumentation) slots. The main board (Part 1) comes with one DAC (Digital to Analog Converter) and a mezzanine card (Part 2) provides an additional DAC.

There is a DDR4 module for each DAC containing all the wave data, markers data, as well as the task, scenario and segment tables.

System timing and data is controlled through a single FPGA and the communication interface to an external PC is done through 8 lanes of PCIe GEN3.

Various HW options can be added to the AWG module, such as a digitizer, 8 extra digital markers and fast segment dynamic jump. Each of these options adds an additional PCB board that occupies an additional PXI slot.

Figure 4.2 Proteus Block Diagram

# 4.4 Modes of Operation

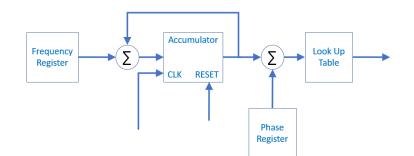

There are four modes that can be used in order to generate a signal with the Proteus AWG. Direct mode, NCO mode, IQ mode and Streaming mode. An explanation on each of the modes follows.

#### 4.4.1 Direct Mode

In the direct mode the signal being generated is coming from the onboard arbitrary waveform memory. Each part of the unit has a DDR4 module where the arbitrary waveforms are stored. When generating in the direct mode the data stored in the DDR4 is transmitted to the DAC and then to the channel output. When there are 2 channels per part the channels share the same waveform memory. The channels can read from the same segment simultaneously.

| Interpolation Factor Waveform Sampling Rate Range DAC Sampling Rate |                 |             |

|---------------------------------------------------------------------|-----------------|-------------|

| x1 (no interpolation)                                               | SCLK            | 1e9 - 2.5e9 |

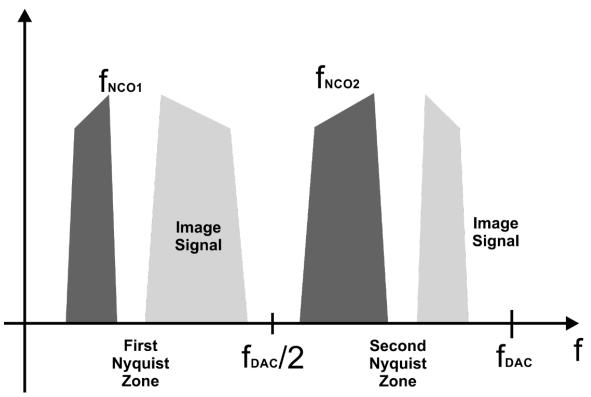

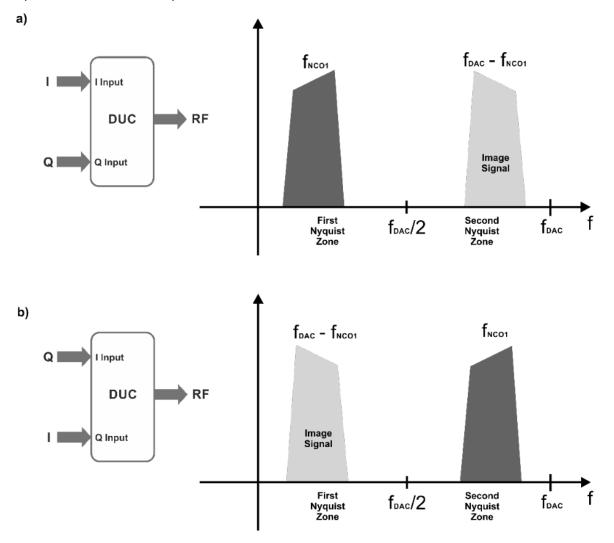

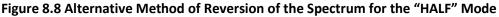

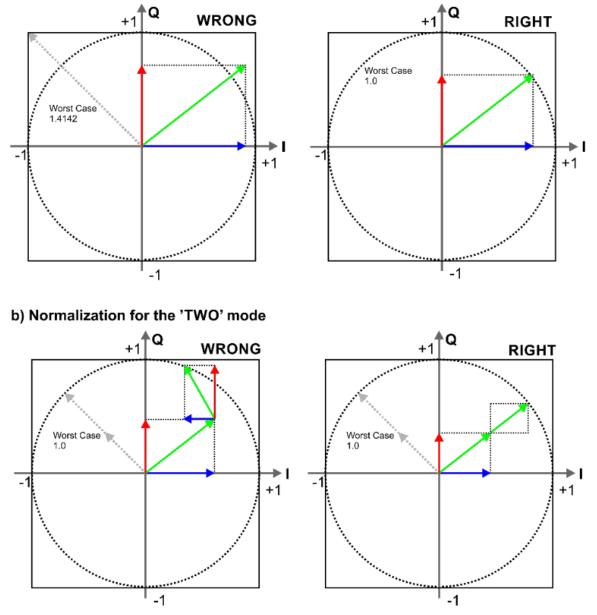

| x2                                                                  | 0.5e9 - 2.5e9   | 1e9 - 5e9   |